|

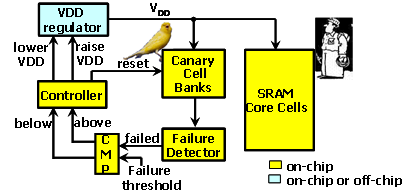

Aggressive scaling according to Moore’s Law, combined with the push to incorporate more functionality and higher performance on a single chip, has created the widely known power problem in modern ICs. Power consumption has become a major limiting factor in many designs. A number of solutions have been preliminarily explored to help improve the energy efficiency of chips, including clock gating, power gating, local voltage regulation, and dynamic voltage scaling. While theoretical benefits of these techniques are known, their full impact on the overall power distribution network remains uncertain. This project aims to address the impact of Panoptic Dynamic Voltage Scaling (PDVS) on the power distribution network and compare them against alternative low power techniques.

|