ViPro for Register Files (RFs) - not only explores methodologies of designing low power and high performance RFs and it also extends a virtual prototyping (ViPro) tool to support fast and efficient estimation of different design knobs on the overall multi-port RF macros. The extension of ViPro fills the blank of the multi-port register files, and provides hierarchical BL scheme as an extra knob for better memory design.

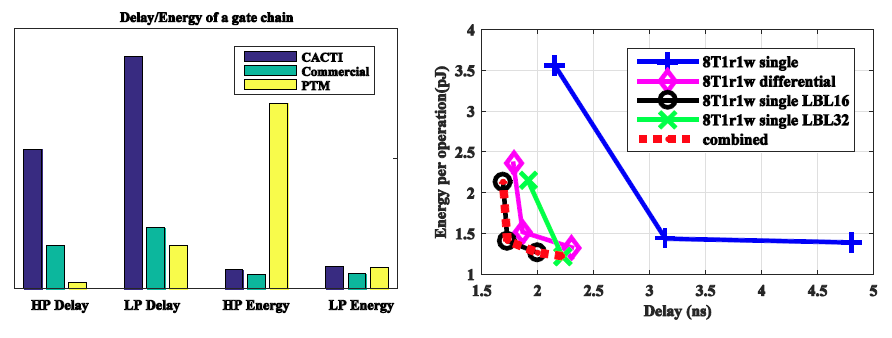

Similar tool likes CACTI developed by HP Laboratories also evaluates delay and energy of memories, but the results are extremely inaccurate due to using a mathematical circuit model. The left figure above illustrates the delay and energy of a gate chain which is a fundamental element of circuits, and results of CACTI using high performance and low power transistors are both substantially different from SPICE simulation results of the commercial technology and the predictive technology model for the same gate chain.

The right figure above shows the Pareto curves of the 8T 1R/1W bitcell with single-ended BL sensing, differential BL sensing, and two hierarchical BL (16bits/LBL & 32bits/LBL) sensing schemes at 8KB capacity. Two hierarchical BL sensing schemes contribute to the combined Pareto curve.