NanoWatt SoC for System-in-Fiber

|

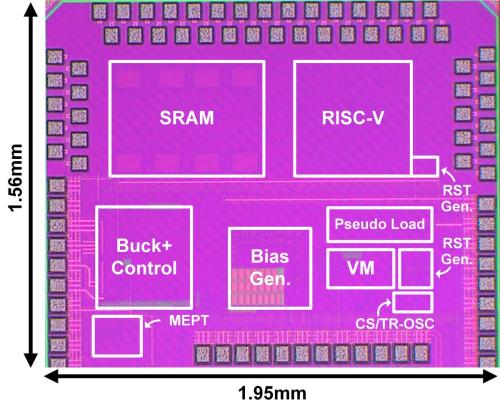

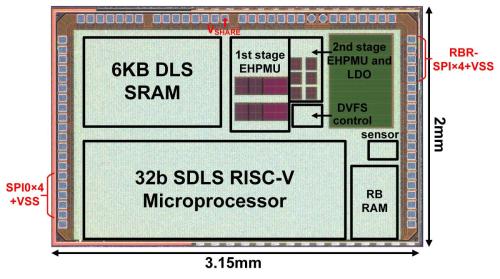

This work presents a fully autonomous system-on-chip (SoC) that can be distributed along a fiber strand, capable of simultaneously harvesting energy, cooperatively scaling performance, sharing power, and booting-up with other in-fiber SoCs for ultra-low-power (ULP) sensing applications. Utilizing a custom switched capacitor energy harvesting and power management unit (EHPMU), the SoC can efficiently redistribute and reuse harvested energy along the fiber. Integrated on-chip, the ULP RISC-V digital core and temperature sensor enable energy-efficient sensing and computation at nanowatt power levels. A dedicated ripple boot-up and cooperative dynamic voltage and frequency scaling (DVFS) further optimize the operation and physical size of the system. Fabricated in 65 nm, measurement results show that the proposed SoC achieves 33 nW power consumption for the whole chip under 92 Lux lighting condition and can reduce control power down to 2.7 nW for the EHPMU. With the proposed power sharing and cooperative DVFS techniques, the SoC reduces the illuminance needed to stay alive by >7× down to 12 Lux. Integrated into a mm-scale polymer fiber, our SoC demonstrates the feasibility of fully autonomous and ULP on-body sensing systems in resource-constrained fiber environments. |

The proposed nanoWatt System-in-Fiber (NanoSiF) that supports distributed harvesting, sensing, processing and communication.